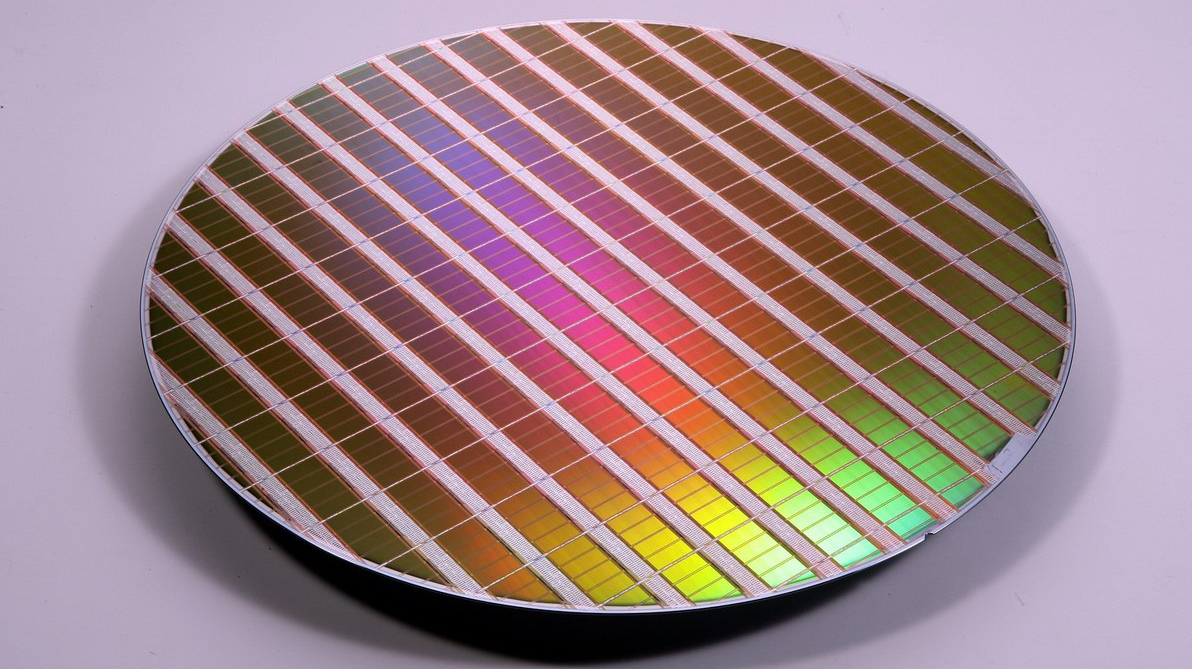

Создана технология сборки многослойных чипов на кремниевой основе

Технологию, позволяющую собирать многослойные микросхемы с кремниевой подложкой на кремниевой несущей пластине, разработали компании IBM и Tokyo Electron, 7 июля сообщает портал о высокопроизводительных вычислениях (HPC) HPCwire.

Все больше разработчиков микросхем используют возможность объемной сборки чипов для увеличения возможностей устройства без изменения площади. Это производится с помощью сборки чипов в несколько слоев.

Процесс обычно производится с использованием стеклянных несущих пластин, поскольку отделить кремниевую подложку микросхемы от кремниевой же несущей пластины ранее было затруднительно. Механическое отделение пластины от подложки приводило к повреждению микросхемы.

Отделение кремниевой подложки микросхемы от стеклянной несущей пластины производится с помощью ультрафиолетовых лазеров. Но у применения стеклянных основ тоже есть свои проблемы — необходимость дополнительного материала в производстве чипов, вероятность формирования дополнительных дефектов, проблемы совместимости материалов.

Компании продемонстрировали возможность сборки многослойных чипов на примере 300 мм пластины на кремниевой основе. Разделение производилось с помощью инфракрасного лазера. Разработчики убеждены, что технология позволит упростить процесс производства многослойных микросхем и снизить себестоимость процесса.