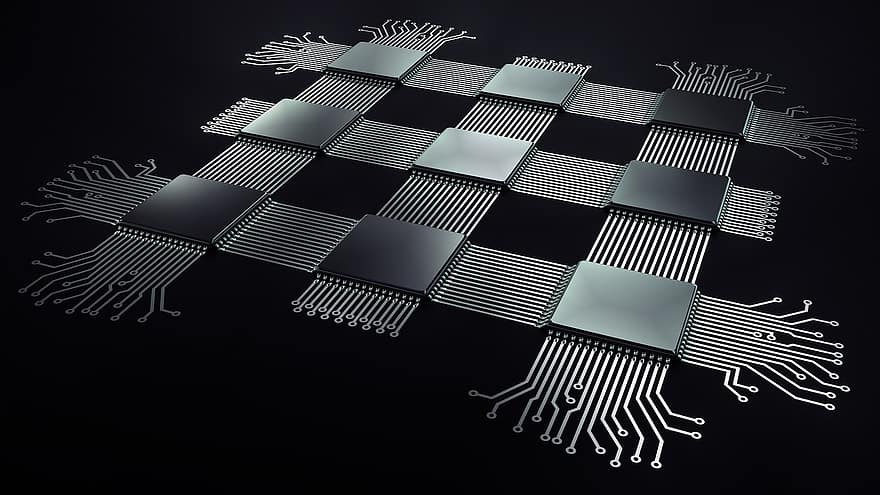

Компания из США представила «процессор иерархического обучения» Ceremorphic

Особенности нового нейроморфного цифро-аналогового процессора Ceremorphic описал генеральный директор одноименной американской компании-разработчика чипа Венкат Маттела 29 января в интервью американскому порталу новостей об информационных технологиях ZDNet.

24 января компания Ceremorphic представила опытный образец нейроморфного ускорителя вычислений. Чип предназначен для обучения и работы систем искусственного интеллекта (ИИ) и является достаточно необычным по архитектуре.

Компания занималась разработкой нейропроцессора в течение двух лет и держала его особенности в тайне. Теперь его представили. Согласно заявлению Маттелы, Ceremorphic одновременно предлагает лучшую на рынке энергоэффективность, устойчивую к взлому систему генерации псевдослучайных чисел и шину взаимодействия с центральным процессором на основе интерфейса PCI-E 6.0, который только утвержден 11 января и еще не нашел где-либо практического применения.

Команда Маттелы долго занималась разработкой электронных решений с высокой энергоэффективностью. Часть команды глава Ceremorphic привлек к работе над новым продуктом. Команда решила обеспечить производительность нейропроцессора не за счет огромного числа цифровых вычислительных узлом, как это сделала, например, Cerebras (их чип Wafer Scale Engine Two, WSE-2 содержит 850 тыс. ядер на площади 45 225 мм²), а за счет применения аналоговых вычислений на низком уровне вычислений в микросхеме.

При этом взаимодействие с программным обеспечением (ПО) осуществляет цифровой слой, что обеспечивает более простую разработку ПО. Такую архитектуру в компании назвали «Hierarchical Learning Processor» (процессор иерархического обучения, HLP). HLP содержит в себе основной вычислительный узел для машинного обучения и отдельный узел для вычислений с плавающей запятой. Оба работают на тактовой частоте 2 ГГц. Микросхема использует специальная разработанный для нее многопоточный планировщик распределения нагрузки.

Взаимодействие с центральным процессором осуществляется через 16 линий интерфейса PCI-E 6.0. Пиковая пропускная способность такого интерфейса составляет 256 Гбайт/с. Взаимодействие по интерфейсу обеспечивает разработанный компанией функциональный блок процессора.

Согласно утверждению Маттелы, в чипе также обеспечена устойчивый к взлому с помощью квантовых вычислительных средств генератор псевдослучайных чисел. Это позволяет обеспечить шифрование с помощью достаточно надежных в ближайшей перспективе ключей.

Еще одной особенностью Ceremorphic в комбинации с разработанным для него ПО стала способность исправлять ошибки вычислений, что обеспечивает устойчивость к сбоям, вызванным, например, космической радиацией.

Нейропроцессор будет сначала поставляться в виде ускорителя для слота PCI-E x16. В дальнейшем планируются и другие варианты. Спроектирован Ceremorphic под техпроцесс 5 нм TSMC, такие изделия будут выпущены в серии в 2024 году. Первые же серии будут изготовлены по более грубому техпроцессу 7 нм и ожидаются в 2023 году.

Заявляется, что процессор можно будет использовать в большом спектре задач, где используется машинное обучение, — робототехнике, автономных автомобилях, центрах обработки данных, вычислительных системах в основе метавселенных и других.