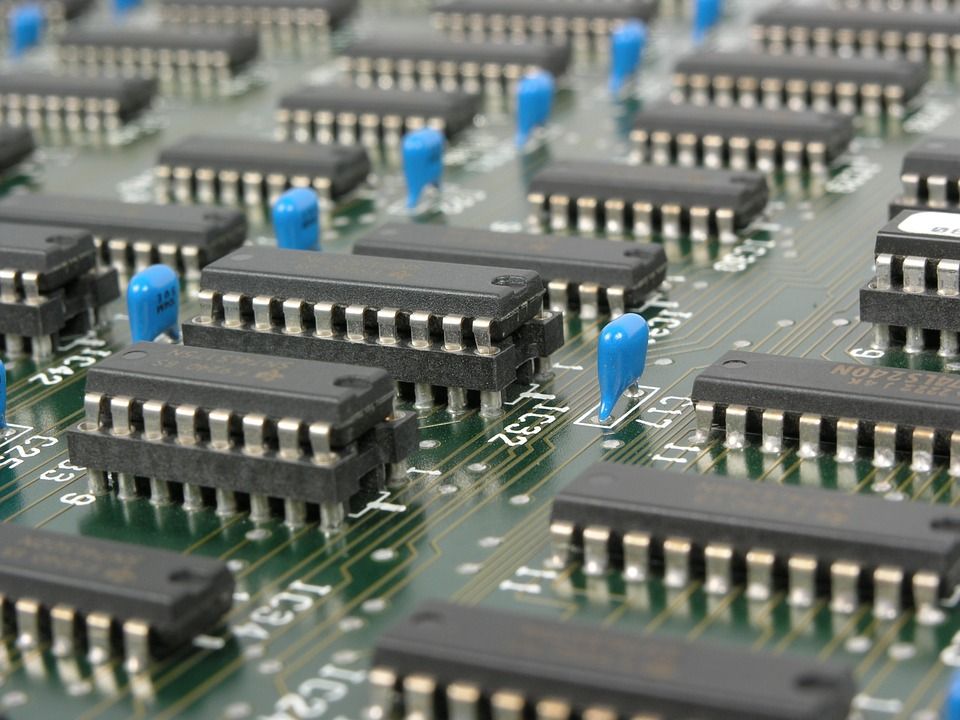

Intel запатентовала новый дизайн транзисторов для техпроцесса менее 2 нм

Новую архитектуру транзисторов «с разветвленными листьями» Stacked Forksheet Transistor запатентовала компания Intel, 23 января сообщает американское интернет-издание о компьютерных технологиях Tom’s Hardware.

Компания планирует использовать такую конфигурацию транзисторов для создания трехмерных структур чипов, чтобы продолжать сохранять действие закона Мура. Согласно эмпирическому наблюдению одного из основателей Intel Гордона Мура, число транзисторов на микросхеме удваивается примерно каждые два года.

В патенте компании сообщается, что дальнейшее сокращение размера транзисторов может привести к издержкам, которые не будут компенсированы потенциальными выгодами в виде увеличения энергоэффективности и производительности.

В новой архитектуре три или более наноленточных транзистора разделяются германиевой пленкой толщиной несколько атомов. Пленка служит диэлектриком между p и n-зонами. Это позволяет увеличить плотность размещения транзисторов за счет использования вертикальной плоскости.

Ожидается, что подобную архитектуру транзисторов Intel может использовать для технологических процессов менее 2 нм. При этом уже применительно к 2 нм техпроцессу дизайн позволяет увеличить тактовую частоту на 10%, либо энергоэффективность на 24%. Площадь «ячейки» кристалла при этом сокращается на 20%. В случае памяти SRAM — на 30%.

Сама идея не нова, впервые компания продемонстрировала подход в 2019 году. Похоже, теперь подобная архитектура начинает становиться все более актуальной.