Запуск опытного производства 3 нм чипов компании TSMC выявил новую проблему

Новая проблема с изготовлением передовых полупроводниковых изделий была выявлена в связи с запуском опытного производства чипов по техпроцессу 3 нм крупнейшим контрактным производителем микросхем Taiwan Semiconductor Manufacturing Company (TSMC), 1 декабря сообщает новостной портал об электронике, автомобилях и индустрии 4.0 TechTaiwan.

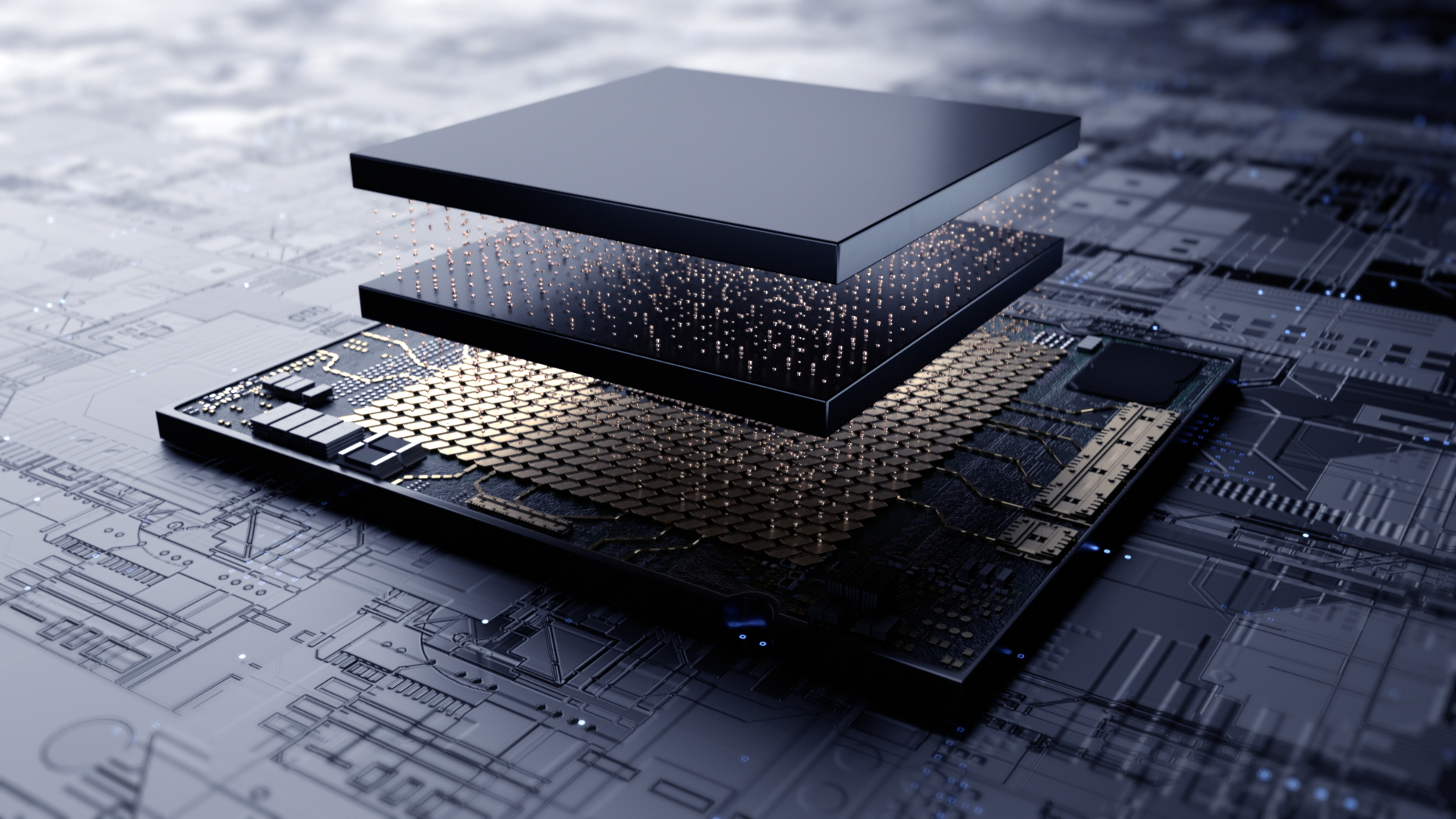

TSMC запустила рисковое производство по техпроцессу 3 нм. Массовое производство предполагается запустить только в четвертом квартале 2022 года. Тем не менее, уже выявлена первая серьезная проблема не в самом процессе изготовления чипов. Проблема выявлена на стадии корпусирования микросхем.

Современные высокопроизводительные вычислительные микросхемы, а именно такие производятся по передовым техпроцессам, совмещают в одном корпусе несколько кристаллов. Кристаллы различного назначения совмещаются уже не только в одной плоскости, но стыкуются по вертикальной оси.

Такая объемная компоновка сложных изделий формирует потребность в огромном количестве соединений между кристаллами внутри корпуса. Отмечается, что с каждым новым поколением техпроцесса шаг контактов должен уменьшаться на 70%. И тут у компании и контрактных корпусировщиков возникают трудности, когда шаг соединения требуется меньше 2 мкм.

В частности, проблема возникла с изготовлением подложек и специальных прослоек-соединителей (интерпозеров). Ожидается, что пока проблему не решат, она может повлиять на заметное увеличение стоимости конечной продукции.